### COS 140: Foundations of Computer Science

### Virtual Memory: Translation Lookaside Buffer

### Fall 2018

| Virtual Memory      | 3  |

|---------------------|----|

| Pages               | 4  |

| Paging              | 5  |

| Page faults         | 6  |

| Page Tables         | 7  |

| Mapping             | 7  |

| Page tables         | 8  |

| Example             | 9  |

| Example             | 10 |

| MMU                 | 11 |

| Address translation | 12 |

| Problems            | 14 |

| Solution            |    |

| ГLВ                 | 17 |

| What is it?         | 17 |

| How it works        | 18 |

| Successful?         |    |

| Multi-Level Paging  | 20 |

| Problem             | 20 |

| Solution            |    |

| Success?            |    |

| Caching Carling     | 23 |

| Homework, announcements |                                                                          |

|-------------------------|--------------------------------------------------------------------------|

|                         | Reading: Chapter "Virtual Memory: Translation Lookaside Buffer" (Ch. 21) |

|                         | Homework: Exercises at end of chapter                                    |

|                         | Due Wednesday, $11/14$ (later than usual)                                |

|                         | NOTE: Prelim II on 11/14                                                 |

|                         | Reminder: Advising!                                                      |

Copyright © 2002–2018 UMaine Computer Science Department – 2 / 23

Virtual Memory 3 / 23

### Virtual memory

- ☐ Goals:

- Allow more processes to run simultaneously (increase degree of multiprogramming)

- Allow very large processes to run

- ☐ Approach:

- Keep most of each process on disk (in paging/swap area)

- Only keep that part of each process in memory that is actually in use

Copyright © 2002–2018 UMaine Computer Science Department – 3 / 23

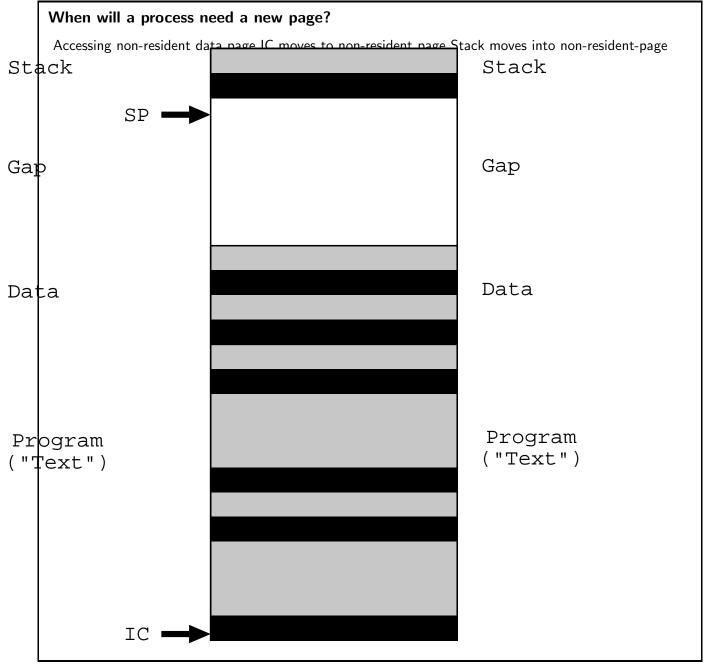

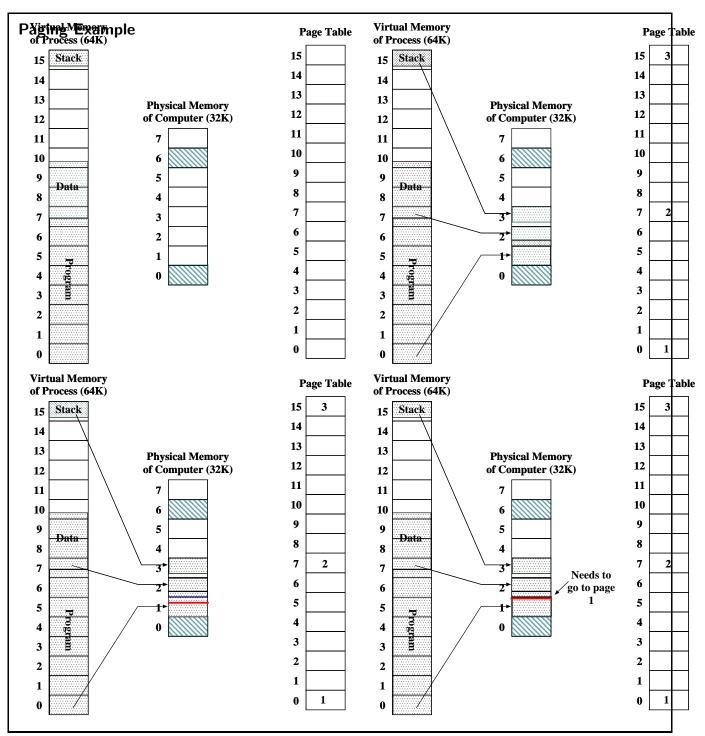

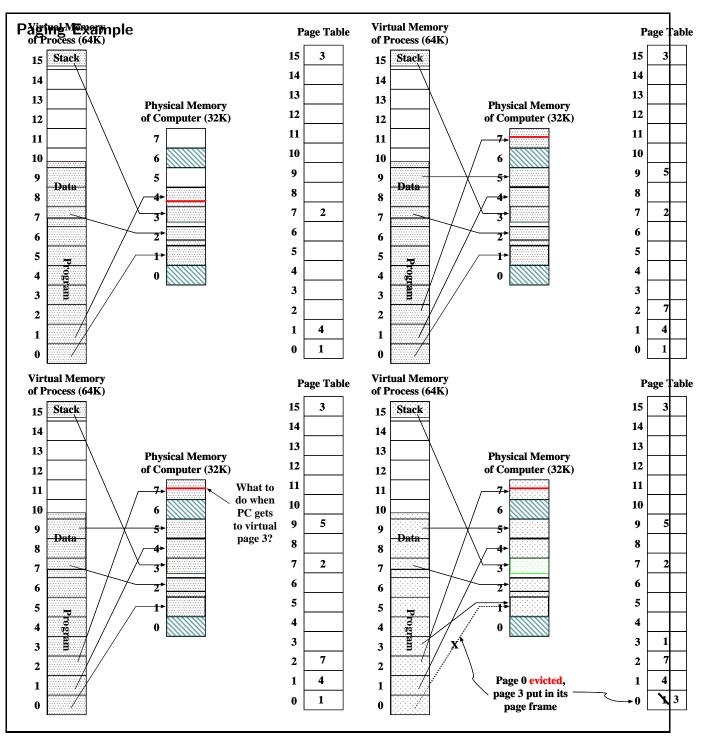

## Pages and page frames □ Divide process' address space into pages of some fixed size – usually 2Kb–4Kb □ Divide (physical) memory into page frames of same size □ Put needed pages of process into page frames: Need not be contiguous

Move pages back and forth between disk and memory as needed: demand paging

Copyright © 2002–2018 UMaine Computer Science Department – 4 / 23

Copyright © 2002–2018 UMaine Computer Science Department – 5 / 23

| Page faults |                                                                                                                                                                       |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             | If page is resident – use it  If page is not resident ⇒ page fault  A page fault is a type of interrupt  Operating system wakes up, tries to bring in the needed page |  |

|             | <ul><li>What if there are free page frames?</li><li>What if there are no free page frames?</li></ul>                                                                  |  |

Copyright © 2002–2018 UMaine Computer Science Department – 6 / 23

Page Tables 7 / 23

| Page⇔frame mapping |                                                                              |

|--------------------|------------------------------------------------------------------------------|

|                    | At any given time, need to keep track of where a process' resident pages are |

|                    | Also need to keep track of which pages are not resident                      |

|                    | Use a <i>page table</i> for this                                             |

|                    | Page table entries (PTEs) map from pages to where those pages live in memory |

Copyright © 2002–2018 UMaine Computer Science Department – 7 / 23

| Pa | Page tables                                                                                                                                             |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    | One page table per process One page table entry per page in virtual memory (address space) Each entry contains:                                         |  |  |

|    | <ul> <li>Present/absent bit</li> <li>Page frame number</li> <li>Dirty bit (M bit)</li> <li>Reference bit (R bit)</li> <li>Maybe other things</li> </ul> |  |  |

Copyright © 2002–2018 UMaine Computer Science Department – 9 / 23

Copyright © 2002–2018 UMaine Computer Science Department – 10 / 23

## Memory management unit ☐ How does a virtual address ⇒ a physical address? ☐ Memory management unit (MMU): piece of hardware that sits between the CPU and memory: CPU wirtual address Memory Memory These days: MMU is on CPU chip

Copyright © 2002–2018 UMaine Computer Science Department –  $11\ /\ 23$

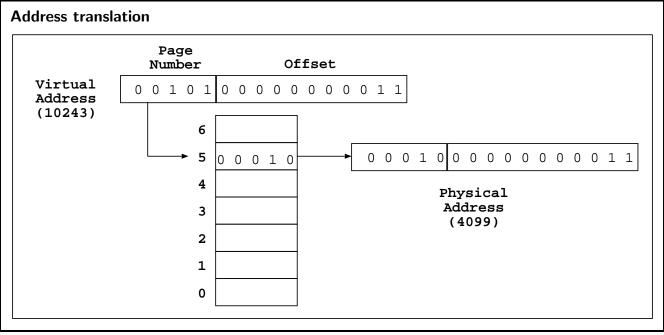

### **Address translation**

- $\hfill\Box$  How does the virtual address get translated to a physical address?

- ☐ Suppose we have 2KB pages, 16-bit machine:

- $2KB = 2^{11}$ bytes need 11 bits to address each byte on a page

- Divide virtual address into 5-bit page number, 11-bit offset

Copyright © 2002–2018 UMaine Computer Science Department –  $12\ /\ 23$

Copyright © 2002–2018 UMaine Computer Science Department – 13 / 23

### Problems with page tables □ Speed of access: - If table lives in memory, then for every memory access, have to look in page table to find address—a memory access itself—then do memory access Effective memory access time is doubled □ Possible solution: Use very fast memory in MMU

Copyright © 2002-2018 UMaine Computer Science Department - 14 / 23

### Problems with page tables

- ☐ But page tables can be very large:

- One entry per page in virtual address

- With 2KB ( $2^{11}$  bytes) pages, 1 word/entry:

- $_{\triangleright}$  16-bit machine:  $2^{16}/2^{11}=2^{5}$  entries  $=2^{5}\times 2=64$  bytes

- 32-bit machines:  $2^{32}/2^{11}=2^{21}$  entries  $=2^{21}\times 2^2=8$ Mb (!) 64-bit machines:  $2^{64}/2^{11}\times 2^3=2^{56}$  bytes (!!)= 67,108,864 GB

- ☐ Realistically, can't afford that much fast memory! At \$6/GB, \$402,653,184...

...per process!

Copyright © 2002–2018 UMaine Computer Science Department – 15 / 23

| Solution: Caching |                                                                                                                                                                                               |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | A <i>cache</i> is fast memory that holds <i>part</i> of what's in slower memory Idea: prevent accessing slower memory by keeping in cache what will be needed soon Cache according to (e.g.): |  |

|                   | <ul><li>recency</li><li>frequency</li><li>predicted next use</li></ul>                                                                                                                        |  |

Copyright © 2002–2018 UMaine Computer Science Department – 16 / 23

**TLB** 17 / 23

### Translation Look-Aside Buffer □ TLB is a cache of page table entries □ TLB lives in MMU and is composed of very fast registers □ Special kind of registers: associative – MMU can look up page table entry corresponding to page

number in one step

Copyright © 2002–2018 UMaine Computer Science Department – 17 / 23

### How it works

- $\square$  When process starts TLB empty, address 0 CPU  $\Rightarrow$  MMU:

- PTE for page 0 not in TLB; read in from page table in memory

- Page 0 not mapped ⇒ page fault

- Page in page 0 into frame i, update PTE in TLB

- □ Next time some address on page 0 referenced:

- Use PTE in TLB to find frame i

- No memory access for PTE

- □ When TLB full:

- Have to eject some PTE from cache

- Write it to page table first

Copyright © 2002-2018 UMaine Computer Science Department - 18 / 23

### How well does it work?

- $\ \square$  Assume memory access time  $t_m=$  100ns; no TLB: 200ns/access

- □ With TLB:

$$T_{eff} = p(t_m + t_r) + (1 - p)(2t_m + t_r)$$

where  $T_{e\!f\!f}$  is effective access time, p is probability of PTE being in the cache (hit ratio), and  $t_r$  is time to look something up in TLB

- $\Box$  With  $t_r=20ns$ , hit ratio 0.5:  $T_{eff}=170 \mathrm{ns}$

- $\Box$  Hit ratio 0.8:  $T_{eff}=$  140ns

- $\Box$  Hit ratio 0.98:  $T_{e\!f\!f}=$  122ns

Copyright © 2002–2018 UMaine Computer Science Department –  $19 \ / \ 23$

### Multiple-level paging

- □ Problem: With large address sizes, page tables too big to keep in memory

- □ Would like to page out the page tables themselves!

- ☐ Can't, with monolithic tables

- ☐ Solution: multi-level page tables

- □ "Outer tables" act as page tables for "inner" pages only outer needs to be resident in memory

- $\square$  Price:  $\geq 2$  memory accesses/access in worst case

Copyright © 2002–2018 UMaine Computer Science Department – 20 / 23

# Multi-level page tables 1. Use first page number (2) to find city is easily page fable. 2. Use that earny's value (16) as page frame number in which to find in page frame number in which to find in page table ended (type table 3). 3. Use the second field in the virtual address (4) to find the correct orang page table ended (type table and the page frame containing our data — i.e., page frame containing our data — i.e., page frame 3 where the data lives. Outer Page Table Page Table Table Physical Memory New Yorks Cal Memory

Copyright © 2002–2018 UMaine Computer Science Department – 21 / 23

| Does TLB still help?                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| □ Suppose we have 4-level paging, 100 ns memory access time, 20 ns TLB time □ Worst case: $500 \text{ns}/\text{access}$ (4 page table accesses + desired access) □ With TLB, hit rate 0.98: $T_{eff} = 188 \text{ ns}$ □ More realistic numbers: $t_r = 1 \text{ ns}, t_m = 60 \text{ ns}$ ; 4-level paging: $T_{eff} = 68.8 \text{ ns}$ □ In case you're interested, the effective memory access time for $n$ -level paging is: |  |

| $T_{eff_n} = nt_r + t_m + n(1-p)t_m$                                                                                                                                                                                                                                                                                                                                                                                             |  |

Copyright © 2002–2018 UMaine Computer Science Department – 22 / 23

**Caching** 23 / 23

| Other kinds of caching |                                               |

|------------------------|-----------------------------------------------|

|                        | Caching shows up many places in OS, elsewhere |

|                        | Processor caching physical memory             |

|                        | Disk block caching for files                  |

|                        | Network file systems                          |

|                        | Virtual memory itself                         |

Copyright © 2002–2018 UMaine Computer Science Department – 23 / 23