### Homework □ Reading: Chapter 9 □ Homework: Chapter 9, exercises 1–4 & 7 □ Due Monday, October 1

Copyright © 2002–2018 UMaine Computer Science Department – 1 / 26

### COS 140: Foundations of Computer Science

### Parallel Registers

### Fall 2018

| Problem.       Solution.         Example.       Example.         Circuits that Remember       Gequential Circuits         SR Latch.       SR Latch.         Characteristic Table.       SR Latch Behavior         How It Works.       10         Resetting.       12         Input is 1 1?.       13         Timing Diagrams.       14         Clocked Latches.       16         Registers.       17 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Solution       6         Example       6         Circuits that Remember       6         Sequential Circuits       7         SR Latch       8         Characteristic Table       9         SR Latch Behavior       10         How It Works       11         Resetting       12         Input is 1 1?       13         Timing Diagrams       14         Clocked Latches       16                       |

| Example  Circuits that Remember Sequential Circuits SR Latch Characteristic Table SR Latch Behavior How It Works Resetting Input is 1 1? Timing Diagrams Clocked Latches                                                                                                                                                                                                                             |

| Sequential Circuits         SR Latch       8         Characteristic Table       9         SR Latch Behavior       10         How It Works       11         Resetting       12         Input is 1 1?       13         Timing Diagrams       14         Clocked Latches       16                                                                                                                       |

| SR Latch       8         Characteristic Table       9         SR Latch Behavior       10         How It Works       11         Resetting       12         Input is 1 1?       13         Timing Diagrams       14         Clocked Latches       16                                                                                                                                                   |

| Characteristic Table       9         SR Latch Behavior       10         How It Works       11         Resetting       12         Input is 1 1?       13         Timing Diagrams       14         Clocked Latches       16                                                                                                                                                                            |

| SR Latch Behavior       10         How It Works       11         Resetting       12         Input is 1 1?       13         Timing Diagrams       14         Clocked Latches       16                                                                                                                                                                                                                 |

| How It Works       1.         Resetting       1.         Input is 1 1?       1.         Timing Diagrams       1.         Clocked Latches       1.                                                                                                                                                                                                                                                    |

| How It Works       1.         Resetting       1.         Input is 1 1?       1.         Timing Diagrams       1.         Clocked Latches       1.                                                                                                                                                                                                                                                    |

| Resetting       12         Input is 1 1?       13         Timing Diagrams       14         Clocked Latches       16                                                                                                                                                                                                                                                                                  |

| Input is 1 1?       15         Timing Diagrams       14         Clocked Latches       16                                                                                                                                                                                                                                                                                                             |

| Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                      |

| Clocked Latches                                                                                                                                                                                                                                                                                                                                                                                      |

| Posistors 1                                                                                                                                                                                                                                                                                                                                                                                          |

| Registers                                                                                                                                                                                                                                                                                                                                                                                            |

| Requirements                                                                                                                                                                                                                                                                                                                                                                                         |

| Construction                                                                                                                                                                                                                                                                                                                                                                                         |

| One Bit                                                                                                                                                                                                                                                                                                                                                                                              |

| Two bits                                                                                                                                                                                                                                                                                                                                                                                             |

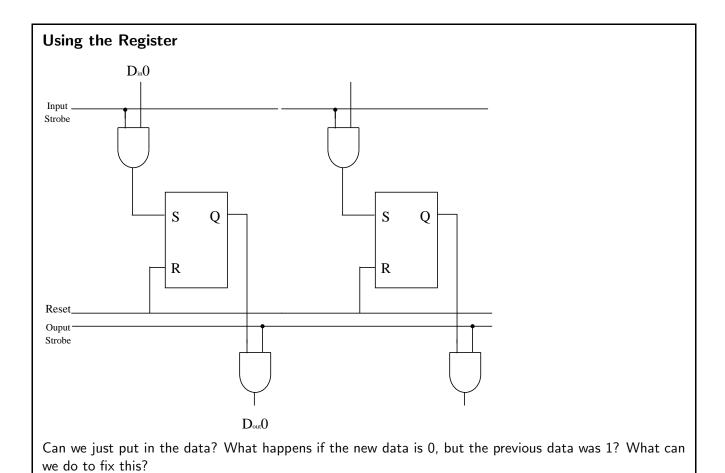

| Using the Register                                                                                                                                                                                                                                                                                                                                                                                   |

| More                                                                                                                                                                                                                                                                                                                                                                                                 |

| Flip-flops                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                      |

| Edge-triggering                                                                                                                                                                                                                                                                                                                                                                                      |

| SR flip-flop                                                                                                                                                                                                                                                                                                                                                                                         |

**Overview** 3 / 26

### Problem

$\hfill\Box$  The central processing unit (CPU) needs some memory

- Place to store instructions being executed

- Place to store instruction's *operands*

- Place to store intermediate values, output of calculations

- $\hfill\Box$  This memory has to be extremely fast: faster than RAM

Copyright © 2002–2018 UMaine Computer Science Department – 3 / 26

## Solution: Parallel Registers □ Use parallel registers □ Very fast type of memory □ Stores several bits at a time, function together as a unit. □ Could be one chip or more than one chip used in parallel □ Most often: part of the CPU

Copyright © 2002–2018 UMaine Computer Science Department – 4 / 26

| A Parallel Registe | er                                          |                                                                                             |                                                         |                                             |                                                             |

|--------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------|

| D                  | REGISTER                                    | D a t a b i t t c v t c d d t t t t t t t t t t t t t t t t                                 | D                                                       | REGISTER                                    | D a t a b i t s O u t                                       |

| D                  | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>REGISTER | 0 D 0 a 0 t 0 a 0 B 0 t 0 t 0 c 0 t 0 c 0 t 0 t 0 c 0 t 0 t 0 t 0 t 0 t 0 t 0 t 0 t 0 t 0 t | D 1                                                     |                                             | 0 D 0 a 0 t 0 a 0 b 0 a 0 B 0 i 0 t 0 s 0 t 0 t 0 t 0 t 0 t |

| D 1                | 0<br>1<br>0<br>0<br>0<br>1<br>1<br>REGISTER | 1 D 0 t 1 a 0 t 1 B 0 i 0 t 0 s 1 U 1 t 0 t 0 t 0 t 0 t 0 t 0 t 0 t 0 t                     | D x a t x a x B x t x x x x x x x x x x x x x x x x x x | 0<br>1<br>0<br>0<br>0<br>1<br>1<br>REGISTER | 1 a 0 t a 1 a 1 B i 0 t t 0 s i 1 O 1 u t                   |

Copyright © 2002–2018 UMaine Computer Science Department – 5 / 26

### WANTED: A Circuit that Can Remember

- ☐ To be useful for memory, the circuit must:

- Be readable.

- Maintain the current data, unless its inputs tell it to change.

- Allow the data to be changed.

- □ Combination circuits have outputs that are a function only of inputs, so no ability to maintain the current data.

Copyright © 2002–2018 UMaine Computer Science Department – 6 / 26

### **Sequential Circuits**

- $\square$  Have state which can be 0 or 1.

- □ New state depends on inputs and previous state.

- ☐ Often have *clock* (strobe, enable) that allows input to enter the circuit only at particular times.

- ☐ Sequential circuits work for memory because

- The current state can be easily read from its output (packaging often makes the state's complement available as well)

- Some set of inputs (usually all 0's) cause it to maintain state

- Other inputs can change the data

Copyright © 2002–2018 UMaine Computer Science Department – 7 / 26

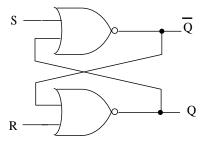

### A Circuit that Can Maintain State: The S-R Latch

- $\Box$  Can be set (with S) and reset (with R)

- □ Maintains whatever state it's set to when inputs removed (set to 0)

Copyright © 2002–2018 UMaine Computer Science Department – 8 / 26

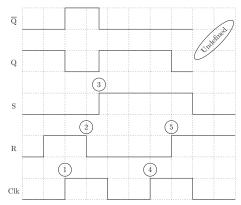

### **Characteristic Table**

- ☐ How to specify the behavior of a sequential circuit?

- ☐ Truth table won't work: doesn't reference current state

- ☐ Instead, use a *characteristic table*; like a truth table, but:

- Shows current state as well as inputs

- Gives new state (which is output as well)

- Note: Can have inputs for which there is no stable state, an undefined state, or a state that does not make sense

Copyright © 2002–2018 UMaine Computer Science Department – 9 / 26

### What Would We Expect?

| S | R | $Q_{n+1}$ |

|---|---|-----------|

| 0 | 0 | $Q_n$     |

| 0 | 1 | 0         |

| 1 | 0 | 1         |

| 1 | 1 | -         |

Copyright © 2002–2018 UMaine Computer Science Department – 10 / 26

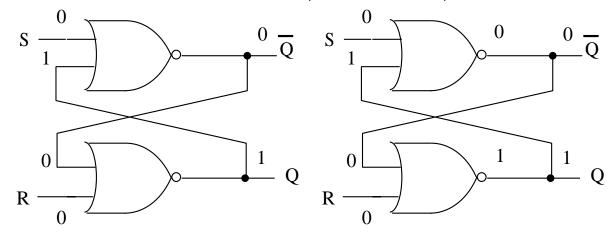

### How the S-R Latch Maintains State

Have feedback from the current state and its complement that act as input to the circuit.

Copyright © 2002–2018 UMaine Computer Science Department – 11 / 26

Copyright © 2002–2018 UMaine Computer Science Department – 12 / 26

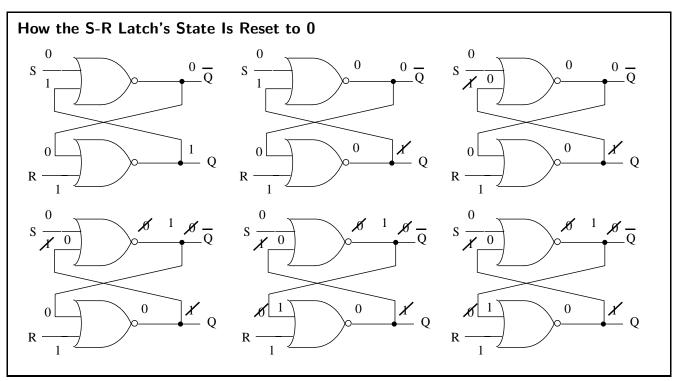

Copyright © 2002–2018 UMaine Computer Science Department – 13 / 26

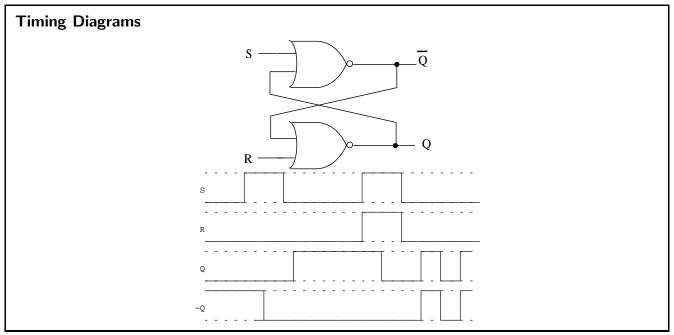

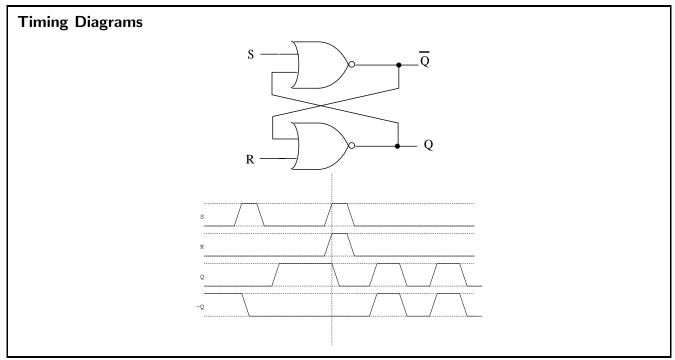

Copyright © 2002–2018 UMaine Computer Science Department – 14 / 26

Copyright © 2002–2018 UMaine Computer Science Department – 15  $\,/\,$  26

| CI | 00 | ked | 1 | 21  | اء  | h | 26 |

|----|----|-----|---|-----|-----|---|----|

| L  | UC | ĸeu | L | .aı | LCI | ш | 25 |

- Sometimes you want the state to change only at certain times.

- ☐ To do this, latches can be hooked to a clock.

- $\Box$  The clock is a signal that is 1 at certain intervals.

- □ Creating clocks in hardware and dealing with timing issues in circuits is a complex problem…beyond the scope of this course.

☐ If clock is not 1, equivalent to S and R of unclocked latch being 0, and maintain state. If clock is 1, value of S and R get through AND gate.

Copyright © 2002–2018 UMaine Computer Science Department – 16 / 26

Registers 17 / 26

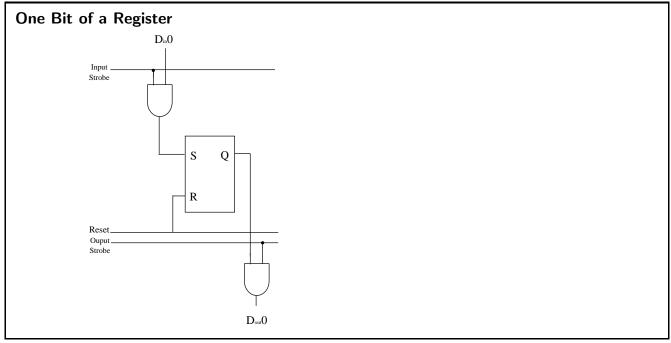

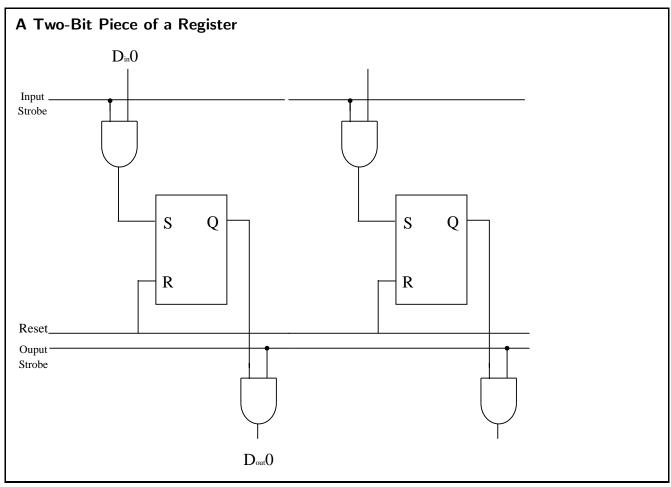

### What Do We Need in a Register?

- ☐ Each bit can be stored in a latch (usually 8 or more)

- □ Nice to be able to reset register to all 0's

- □ Output available from each bit

- □ Input can be directed to each bit

Copyright © 2002–2018 UMaine Computer Science Department – 17 / 26

### How Can We Construct a Register?

- $\Box$  We can use S-R Latches and simply make sure S and R are not both 1 at the same time.

- $\square$  Have a reset line that goes to R in each latch.

- □ "Strobe" input and output so that write or read data only at specific times. (Works similarly to a clock.)

Copyright © 2002–2018 UMaine Computer Science Department – 18 / 26

Copyright © 2002–2018 UMaine Computer Science Department – 19 / 26

Copyright © 2002–2018 UMaine Computer Science Department – 20 / 26

Need to reset each time before loading data.

Copyright © 2002–2018 UMaine Computer Science Department – 21 / 26

### More About Latches and Registers

- ☐ There are other kinds of latches which:

- Do not require resetting register before loading data so can toggle individual bits

- Handle the problem of 1–1 inputs

- ☐ Registers can be constructed out of these latches, as well.

Copyright © 2002–2018 UMaine Computer Science Department – 22 / 26

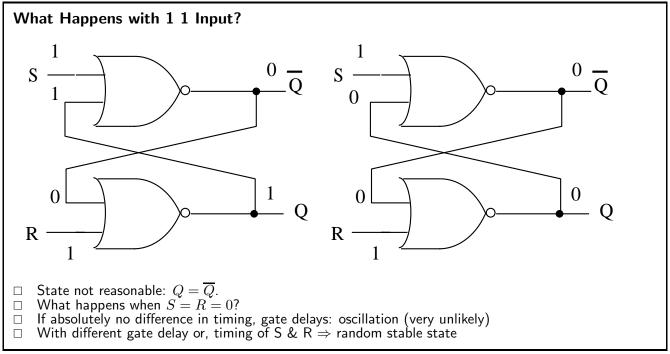

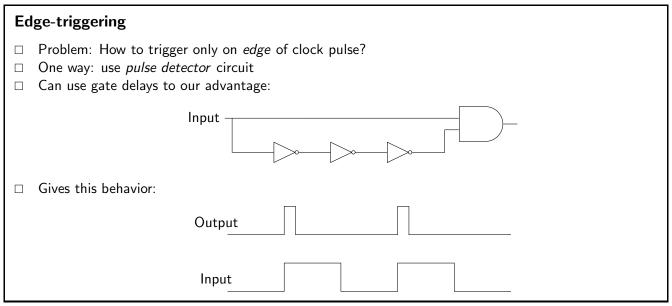

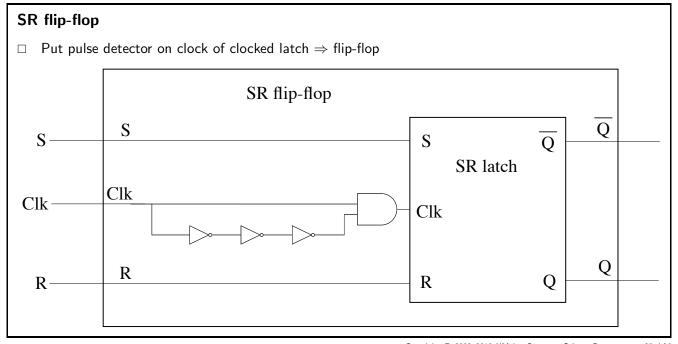

### Flip-flops

- □ So far: *latches* − *level-triggered*

- □ Problem:

- Only want changes once per clock pulse

- But: clock pulse can be long ⇒ time for inputs to change

- Could lead to unwanted states: e.g., 1–1 to SR latch

- □ Solution: *edge-triggering*

- $\square$  Edge-triggered latch  $\equiv$  flip-flop

Copyright © 2002–2018 UMaine Computer Science Department – 23 / 26

Copyright © 2002–2018 UMaine Computer Science Department – 24 / 26

Copyright © 2002–2018 UMaine Computer Science Department – 25 / 26

# Edge triggering: master-slave configuration $\square \quad \text{Can also get edge triggering by using two latches:}$ $S_{in} \qquad S \qquad Q \qquad S \qquad Q_{out}$ $Clock \qquad Clk \qquad R \qquad \overline{Q} \qquad \overline{Q}_{out}$

Copyright © 2002–2018 UMaine Computer Science Department – 26 / 26