#### COS 140: Foundations of Computer Science

#### CPU Organization and Assembly Language

#### Fall 2018

| СРИ                          | 3  |

|------------------------------|----|

| Components of the CPU        | 4  |

| Registers                    | 5  |

| Register design issues       | 6  |

| Assembly Language            | 8  |

| Machine Language             | 8  |

| Assembly Language            | Ç  |

| Instruction Execution        | 10 |

| Instruction Format           | 11 |

| Instruction Types            | 12 |

| Types of Instructions        | 12 |

| Data Transfer Instructions   | 13 |

| Arithmetic Operations        | 14 |

| Logical operations           | 15 |

| Transfer of control          | 16 |

| System control               | 17 |

| Number of Instructions       | 18 |

| Data Types                   | 20 |

| Addressing Modes             | 21 |

| Addressing Modes             | 21 |

| Immediate Addressing         | 22 |

| Direct Addressing            | 23 |

| Direct Addressing            | 24 |

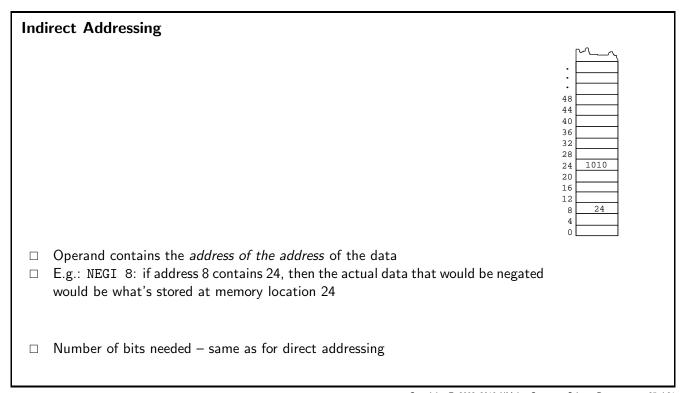

| Indirect Addressing          | 25 |

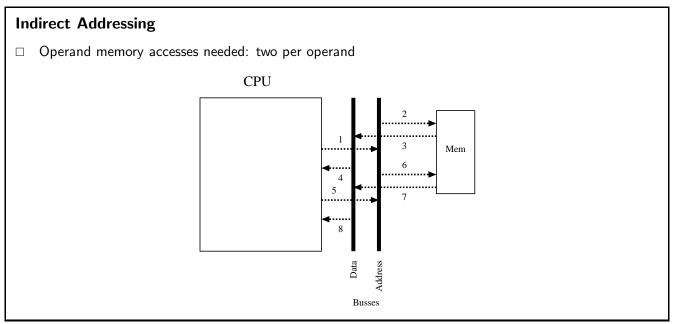

| Indirect Addressing          | 26 |

| Register Addressing          | 27 |

| Register Indirect Addressing | 28 |

| Other Addressing Modes       | 29 |

| Instruction Set Design       | 30 |

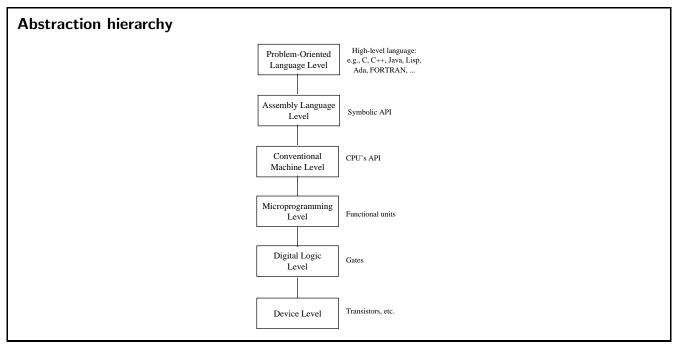

| Abstraction                  | 31 |

| Abstraction hierarchy |  | 3. |

|-----------------------|--|----|

|-----------------------|--|----|

| Н | Homework, etc.                                                                                                                                                           |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | Reading                                                                                                                                                                  |  |  |

|   | <ul><li>Chapter 14</li><li>Appendix A is there as well</li></ul>                                                                                                         |  |  |

|   | Homework: Exercises at end of Chapter 14, due $10/17$ (later than usual) Prelim I: Friday, $10/12$                                                                       |  |  |

|   | <ul> <li>Detailed questions (e.g., problems) on material up through RAID</li> <li>Conceptual questions on all material up to &amp; including today's material</li> </ul> |  |  |

Copyright © 2002–2018 UMaine Computer Science Department – 2 / 31

**CPU** 3 / 31

#### **Central Processing Unit**

- $\hfill\Box$  Part of the computer that carries out the instructions of programs

- $\Box$  Controls the other two parts (memory, I/O).

- ☐ This class:

- CPU organization

- Machine (and assembly) language introduction

Copyright © 2002–2018 UMaine Computer Science Department – 3 / 31

#### Components of the CPU

Arithmetic and logic unit (ALU): where actual computation takes place

Control unit (CU): controls moving information around in CPU, placing data in registers, getting new instructions from memory, ALU function, etc.

Registers: memory for CPU operation

Copyright © 2002–2018 UMaine Computer Science Department – 4 / 31

#### Registers

- ☐ Registers virtually all CPUs have:

- program (or instruction) counter

- program status word (PSW)

- instruction register

Copyright © 2002–2018 UMaine Computer Science Department – 5 / 31

# Design Issues for Registers ☐ User accessible or protected? ☐ Want to protect the machine, other users from the user ☐ PSW — probably protected ☐ Instruction counter: generally protected, but some special instructions for changing (e.g., branch, subroutine instructions)

Copyright © 2002–2018 UMaine Computer Science Department - 6 / 31

#### **Design Issues for Registers**

- ☐ General-purpose or special-purpose?

- General-purpose  $\Rightarrow$  flexibility

- Special-purpose ⇒ reduce number of operands or operand size

- Mixed: some special-purpose registers that are used as general-purpose registers by some instructions

- Different size registers for different purposes

Data registers: user accessible (via instructions)

- □ Size?

- Need to hold largest operand required

- Sometimes use multiple registers for single operand

- □ Who saves them when needed (on interrupt) software or hardware?

Copyright © 2002–2018 UMaine Computer Science Department – 7 / 31

| Machine Language |                                                 |  |

|------------------|-------------------------------------------------|--|

|                  | Instruction set: instructions CPU can carry out |  |

|                  | Each: Op code $\& \ge 0$ operands               |  |

|                  | Operands include addresses and data.            |  |

|                  | Op codes, operands: binary numbers—of course.   |  |

|                  | Instuctions are the machine language            |  |

|                  | Difficult for humans to use!                    |  |

Copyright © 2002–2018 UMaine Computer Science Department – 8 / 31

#### **Assembly Language**

- ☐ Symbolic version of machine language.

- $\Box$  Op codes represented by *mnemonics* e.g.,

- Machine language: addition op code might be 001001

- Assembly language: might represent as ADD

- Operands can be symbolic: names for constants, memory locations

- Assembler translates assembly language program ightarrow machine language

Copyright © 2002–2018 UMaine Computer Science Department – 9 / 31

| Instruction Execution |                               |  |

|-----------------------|-------------------------------|--|

|                       | Fetch instruction from memory |  |

|                       | Decode instruction            |  |

|                       | Fetch operands (if any)       |  |

|                       | Carry out instruction         |  |

|                       | Store results (if any)        |  |

Copyright © 2002–2018 UMaine Computer Science Department – 10 / 31

#### **Instruction Format**

- $\square$  Specification of action to be done: op code

- □ Addresses of any operands

- $\ \square$  Address of any result to be stored

- $\hfill\Box$  E.g., add register 0 to register 1

- Assembly lang: ADD RO,R1

- Instruction: 01000 | 000 | 0000 | 00 | 01

- 5 bit op code, 3 bits unused, 4 bits for mode (direct, direct), R0, R1

Copyright © 2002–2018 UMaine Computer Science Department – 11 / 31

Instruction Types 12 / 31

| Types of Instructions |                       |  |

|-----------------------|-----------------------|--|

|                       | Data transfer         |  |

|                       | Arithmetic operations |  |

|                       | Logical operations    |  |

|                       | Transfer of control   |  |

|                       | System control        |  |

Copyright  $\odot$  2002–2018 UMaine Computer Science Department – 12 / 31

#### **Data Transfer Instructions**

- $\square$  Move data from place to place

- ☐ Source, destination could be registers, memory

- □ Different addressing modes possible (see later)

- ☐ Size of transfer: on some machines, amount can be large

Copyright © 2002–2018 UMaine Computer Science Department – 13 / 31

| ☐ Almost all CPUs (i.e., their ALUs) provide ADD, SUB, MULT, and DIV                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ☐ Why include SUB — could use ADD and complement second op?                                                                                                            |

| ☐ Usually provide for signed integers, other types (e.g., floating point)☐ Usually have to move the operand's data to location where ALU expects it (e.g., a register) |

Copyright © 2002–2018 UMaine Computer Science Department – 14 / 31

| Lo | Logical operations                                                                                    |  |  |

|----|-------------------------------------------------------------------------------------------------------|--|--|

|    | Usually provide AND, OR, NOT, XOR, EQUAL, SHIFT, ROTATE, maybe arithmetic shift (sign bit propagated) |  |  |

|    | Why include all these, when you can do it all with NAND?                                              |  |  |

|    | What about complement? Can you do it with XOR? with NOT?                                              |  |  |

|    | How would you mask (clear) particular bits?                                                           |  |  |

|    | How would you set particular bits?                                                                    |  |  |

Copyright © 2002–2018 UMaine Computer Science Department – 15 / 31

| Tr | Transfer of control                                                          |  |  |

|----|------------------------------------------------------------------------------|--|--|

|    | Branch (jump) instructions                                                   |  |  |

|    | <ul><li>Unconditional and conditional</li><li>Absolute or relative</li></ul> |  |  |

|    | Subroutine call and return                                                   |  |  |

Copyright © 2002–2018 UMaine Computer Science Department – 16 / 31

## System control □ Protected operations – only executable by some processes (e.g., operating system) □ Use to access protected registers, protected memory, etc. □ Input/output instructions are usually protected

Copyright © 2002–2018 UMaine Computer Science Department – 17 / 31

#### **Number of Instructions**

- ☐ One philosophy: have relatively few, simple instructions

- Allows instructions to be optimized

- Requires less chip space (⇒ cheaper, or more other things can be put on chip)

- Components can be closer to each other (⇒ faster)

- Reduced instruction set computers (RISC)

- Examples: SPARC chips in Sun machines, PowerPC in older Macs

Copyright © 2002–2018 UMaine Computer Science Department – 18 / 31

#### **Number of Instructions**

- □ Other philosophy: have a large number of instructions, including special-purpose ones (e.g., multimedia, etc.)

- Makes it easier for programmers

- Requires less memory, less disk space for programs

- Complex instruction set computers (CISC)

- Examples: Intel family of processors

Copyright © 2002–2018 UMaine Computer Science Department –  $19\ /\ 31$

| Data Types |                                                                                                                                                                                                                |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|            | Numbers:                                                                                                                                                                                                       |  |

|            | <ul> <li>Integers (sign-magnitude, 2's complement, packed decimal)</li> <li>Floating point</li> <li>Size: single, double, etc.</li> </ul>                                                                      |  |

|            | Characters:                                                                                                                                                                                                    |  |

|            | <ul> <li>Encoded as ASCII or Unicode characters these days</li> <li>Single byte (ASCII) or two or more bytes (Unicode) in length</li> <li>Strings of characters: length + string or null-terminated</li> </ul> |  |

|            | Logical data General bit strings: e.g., for multimedia, etc.                                                                                                                                                   |  |

Copyright © 2002–2018 UMaine Computer Science Department – 20 / 31

#### **Addressing Modes**

21 / 31

#### **Addressing Modes**

- □ Different instructions have different addressing *modes*

- Determines where the data corresponding to the operands is

- ☐ E.g.: think of operand as *name* of data's location

- □ Modes: immediate, direct, indirect, register, register indirect, displacement, others

- ☐ Issues:

- Which one should CPU use for instruction?

- Sometimes indicated by op code

- ▶ Sometimes indicated by *mode bits* that can be set

- How many bits are required for instruction?

- How many memory references are required to find *effective address* (where the data is actually located)?

Copyright © 2002–2018 UMaine Computer Science Department – 21 / 31

| lm | Immediate Addressing                                                                                                                                 |  |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    | Operand's data is the operand itself: i.e., in instruction E.g., NEG $\#5$ might mean "negate 5, leave result in register 0" How many bits needed?   |  |  |

|    | <ul> <li>Generally: fixed-size field in the instruction for operand</li> <li>Generally limited to integers (2's complement) or characters</li> </ul> |  |  |

|    | Operand memory accesses: none                                                                                                                        |  |  |

Copyright © 2002–2018 UMaine Computer Science Department – 22 / 31

#### **Direct Addressing**

- ☐ Operand contains *memory address* of the data

- $\hfill\Box$  E.g.: NEG 8: negate the value of the data <code>located</code> at memory location 8

- □ Number of bits needed?

- Varies between computers, maybe between instructions

- With n bits devoted to address, can refer to  $2^n$  addresses in memory

- Up to size of word

Copyright © 2002–2018 UMaine Computer Science Department – 23 / 31

###

Copyright © 2002–2018 UMaine Computer Science Department – 24 / 31

Copyright © 2002–2018 UMaine Computer Science Department – 25 / 31

Copyright © 2002-2018 UMaine Computer Science Department - 26 / 31

#### Register Addressing

- $\Box$  Implicit  $\Leftarrow$  op code specifies which register is used

- ☐ Explicit ← operand specifies which register

- E.g.: NEG R5 negate the data contained in register 5

- □ Number of bits needed? Usually few, since number of registers limited.

- □ Operand memory accesses: none

- Only requires access to register, which is quick

- Only really efficient if register used over and over otherwise, have to load the register, which could be more inefficient than direct addressing

- □ RISC machines make heavy use of register addressing e.g., PowerPC forces this for all arithmetic operations

Copyright © 2002–2018 UMaine Computer Science Department – 27 / 31

| Register Indirect Addressing |                                                                                               |  |

|------------------------------|-----------------------------------------------------------------------------------------------|--|

| □R                           | Register contains address of the data                                                         |  |

| □ E                          | g.: NEGI R5 — if register 5 contains the value 24, then the data would be found at address 24 |  |

| □ N                          | Number of bits needed? Same as register addressing                                            |  |

| □ C                          | Operand memory accesses: one per operand access                                               |  |

| □ V                          | Vhen would this be useful?                                                                    |  |

Copyright © 2002–2018 UMaine Computer Science Department – 28 / 31

#### Other Addressing Modes

- $\square$  Relative displacement addressing: used for jumps (branches) relative to program counter

- □ Base register displacement addressing: have a base register to which all addresses are added

Copyright © 2002–2018 UMaine Computer Science Department – 29 / 31

#### **Designing Instruction Sets**

- ☐ Which operations to support

- Memory-mapped I/O or special instructions?

- How many instructions to support? RISC or CISC?

- ☐ Format of instructions:

- Size of instruction: part of word, word, multiple words?

- All instructions same size or not?

- Fields within instruction?

- All instructions with same format or not?

- Address modes?

- Number of registers?

- Addressing granularity?

Copyright © 2002–2018 UMaine Computer Science Department – 30 / 31

#### **Abstraction** 31 / 31

Copyright © 2002–2018 UMaine Computer Science Department – 31 / 31